RESEARCH ARTICLE **OPEN ACCESS**

# A Novel VLSI Design of High-Performance **Multiplier Using Latest Trending Adders**

<sup>1</sup>B.Sreenivasan(Assistant)<sup>2</sup>M.Charitha <sup>3</sup>Y.Anitha <sup>4</sup> V.Ivothsna <sup>5</sup>N.R.Charan

Department of Electronics and Communication Engineering Annamacharya Institute of Technology and Sciences, Venkatapuram, Karakambadi, Tirupati

#### **ABSTRACT**

The execution of increase as far as speed and power is vital for the vast majority of the Digital Signal Processing (DSP) applications. Numerous analysts have concocted different multipliers, for example, cluster, Booth, convey spare, Wallace tree and changed Booth multipliers. In any case, for the present day applications Vedic multipliers in view of Vedic Mathematics are by and by under concentration because of their rapid and low power utilization. In this paper, we propose a plan of 8 – bit multipliers utilizing quick adders (convey spare viper, kogge-stone snake and convey select snake) to limit the power defer result of multipliers expected for high performance applications. Execution comes about show that the proposed Vedic multipliers with quick adders truly accomplish critical change in deferral and power-postpone item when contrasted and the ordinary multipliers.

Used Techniques—Vedic multiplier, convey spare exhibit, powerdelay item, convey select viper, kogge-stone snake

## I INTRODUCTION

Multipliers assume critical part in numerous DSP applications, for example, convolution, Fast Fourier Transform (FFT), Discrete Cosine Transform (DCT) and separating. The speed of the DSP's to a great extent relies upon the multiplier square. This thus builds the interest for rapid multipliers. In the course of recent years, numerous scientists have created different multipliers utilizing a few calculations, for example, exhibit, Booth, convey spare, Wallace tree and

changed Booth calculations. Various multiplier designs likewise have been proposed in view of

these calculations that incorporate parallel, serial and serial-parallel multipliers.

In the Wallace tree method, three bit signals are passed to a one bit full adder ("3W") which is called a three input Wallace tree circuit, and the output signal (sum signal) is supplied to the next stage fulladder of the same bit, and the carry output signal thereof is passed to the next stage full adder of the same no of bit, and the carry output signal thereof is supplied to the next stage of the full adder located at a one bit higher position. The major improvement in the multipliers is by reducing the number of partial products generated. The Booth multiplier and modified Booth encoded Wallace

tree (MBW) are such multiplier that, reduces the number of adders. However, the multiplication process involves various intermediate operations that include comparisons, additions and subtractions which reduces the speed as the width of multiplier and multiplicand increases.

The Booth recording multiplier is one such multiplier; it scans the three bits at a time to reduce the number of partial product. These three bits are: the two bit from the present pair; and a third bit from the high order bit of an adjacent lower order pair. After examining each triplet of bits, the triplets are converted by Booth logic into a set of five control signals used by the adder cells in the array to control the operations performed by the adder cells.

The technique for Booth recording diminishes the quantities of adders and thus the postpone required to deliver the halfway entireties by analysing three bits at any given moment. The superior of Booth multiplier accompanies the downside of energy utilization. The explanation behind this is the substantial number of viper cells (15 cells for 8 columns 120 center cells) that expend control. The conclusion is that the present technique of duplication prompts more utilization of energy and diminishment in effectiveness.

To beat the disservice regarding rate of the aforementioned calculations, displayed another multiplier configuration approaches in light of Vedic Mathematics. The fractional items are figured ahead of time and after that additional in view of the Vedic Math way to deal with get the last item. Besides to upgrade the speed of multiplier, in creators have displayed new plans, where the fractional items are included by utilizing swell convey snake, convey spare viper and convey look forward snake . A compressor based Vedic multiplier (CVM) has been outlined, to additionally improve the speed by supplanting the full adders and half adders with compressors. Be that as it may, in the present applications one of the significant difficulties for superior DSP applications is the power dispersal, both static and dynamic. In this way, there is a need to locate an ideal amongst speed and power, rather than focusing on them autonomously. This is spoken to by the normal vitality disseminated for one exchanging occasion and it is known as power-postpone item.

In this paper, the incomplete results of the multiplier are included by utilizing quick adders (convey spare viper, kogge-stone snake and convey select viper) to accomplish deferral and power-proficiency. Test comes about demonstrate that the proposed multiplier with quick adders can accomplish critical change in deferral, and power-postpone item when contrasted with quicker multipliers proposed up to now like stall multiplier and a multiplier with brent-kung snake.

In Section 2, we talk about the Urdhva Tiryakbhyam (vertical and across) strategy for augmentation utilizing Vedic maths in detail. Segment 3 depicts the proposed Vedic multiplier that includes the fractional items utilizing convey spare snake, kogge-stone viper and convey select viper. The execution comes about for various multipliers are displayed in Section 4. At last, Section 5 exhibits a conclusion.

## II. VEDIC MATHEMATICS – URDHVA TIRYAKBHYAM SUTRA

Vedic Mathematics is an old and prominent approach which is essentially in view of 16 Sutras managing different branches of science like number-crunching, variable based math, trigonometry, expository geometry and so forth. To perform increase, a standout amongst the most favoured calculation among these 16 Sutras is the Urdhva Tiryakbhyam Sutra. The words Urdhva and Tiryakbhyam are gotten from Sanskrit which mean verticality and across separately.

The primary favourable position of using this calculation in examination with the current augmentation procedures is that, the fractional items required for increase are created in parallel. These incomplete items are included such a path, to the point that spares a ton of preparing time. This calculation is material for the duplication of paired numbers, so we have picked this Sutra for usage of Vedic multiplier. Give us a chance to consider two

sources of info X1 X0 and Y1 Y0, every one of 2 bits. P3 P2 P1 P0 speaks to each piece of the last processed item. The outcome is gotten in the wake of creating incomplete items and including them according to the essential technique for increase demonstrated as follows.

X1 X0 × Y1 Y0 ------X1Y0 X0Y0 X1Y1 X0Y1

P3 P2 P1 P0

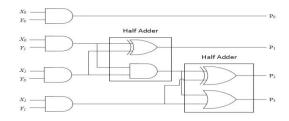

In Vedic arithmetic, the vertical duplication of bits X0 and Y0 gives item P0. The item term P1 is gotten by the expansion of transversely bit augmentation i.e. X1 and Y0 and X0 and Y1. P2 is expansion of the vertical result of bits X1 and Y1 alongside the convey produced from the past expansion amid P1. P3 yield is the convey produced from the past computation of P2. Fig. 1 demonstrates the module that produce 4 yields from the two 2-bit contributions by utilizing AND doors and half viper and it is known as 2x2 multiplier square. This is like move and include system in any case, to additionally enhance the execution of the multiplier, separate and vanquish procedure is utilized for higher bits. Presently, let us break down for a 4×4 augmentation that gives yield item as P7P6P5P4P3P2P1P0.

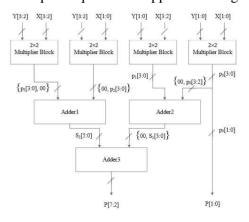

The multiplicand and multiplier are decayed novel strategy has been introduced by supplanting similarly as XH = X3X2 and XL = X1X0 for X and the adders with compressors. In any case, the YH = Y3Y2 and YL = Y1Y0 for Y, where H and L power-defer result of this outline is more. To limit speaks to higher and bring down request bits of X the power-defer item, we proposed multiplier where and Y. Fig. 2 demonstrates the 4 bit augmentation the fractional items are included utilizing quick by taking good for nothing at once and utilizing  $2\times 2$  adders, which are examined in the following multiplier square. As indicated by Vedic arithmetic, segment.

which gives fractional item yields p0[3:0]. At that point, the center one shows across increase of two,  $2 \times 2$  multiplier with inputs XH and YL and XL and YH, creates p1[3:0] and p2[3: 0] fractional item yields separately. At long last, the last square information sources XH& YH increases vertically and creates the halfway item yields as p3[3:0]. The initial two last item yields P0 and P1 are same as that of the halfway items p0[0] and p0[1]. The rest of the item terms are gotten by utilizing three regular adders as appeared in Fig. 3. The contributions for adder1 are  $\{p3[3:0],00\}$  and  $\{00,p2[3:0]\}$  and for adder2 are p1[3:0] and  $\{00,p0[3:2]\}$ . The yields of adder1 and adder2 are offered contributions to the adder3, that creates the last item terms P[7 : 2]. Therefore, the last item terms are gotten by parallel duplication utilizing sub

at first vertical augmentation of XL and YL is done,

Fig1:2X2BinaryMultiplier

Fig2: Square Diagram Representation of 2 X 2 and 4 X 4 multipliers

## III. DESIGN OF PROPOSED 8-BIT VEDIC MULTIPLIER

In this segment we stretch out the Vedic calculation to plan a 8-bit multiplier utilizing quick adders, which can include the incomplete items with a fast and lessens the power delay item. The outline of a

multiplier

squares

and

P7P6P5P4P3P2P1P0, that can diminishes the

postponement of the multiplier. In the above plan the fractional items are included utilizing parallel expansion of full adders and half adders. To additionally enhance the speed of the outline a

expansion

as

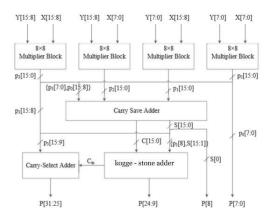

## 8x8 multiplier square is as appeared in Fig. 4.

Fig. 3. Square chart of 4×4 Vedic multiplier

Fig. 4. Proposed 8-bit Vedic multiplier

To acquire  $8 \times 8$  multiplier obstruct, the multiplicand and multiplier bits are disintegrated similarly as XH=X7X6X5X4 and XL=X3X2X1X0 for X and YH=Y7Y6Y5Y4 and YL=Y3Y2Y1Y0 for Y as appeared in Fig. 5. The initial four last item yields P[3:0] are same as that of the halfway items p0[3:0]. The other halfway items which incorporates p1[7:0], p2[7:0] and  $\{p3[3:0], p0[7:0]$ 4]} are included utilizing convey spare snake which can creates the aggregate and convey yield bits as S[7:0] and C[7:0] separately. The item yield P[4]

is the yield of whole S[0]. At that point, the aggregate and convey bits of convey spare snake are included by utilizing kogge-stone viper alongside the fractional item bit p3[4] that creates the last item term P[12:5] and a convey bit Cin.

Fig. 5 convey select snake for 8-bit Vedic multiplier

The last phase of expansion is finished by utilizing carry select viper that multiplexers and half adders as appeared in Fig. 5. On the off chance that the contribution of the convey select snake is Cin=0, the multiplexer gives the contribution of the halfway item yield p3[15:9] to the last item terms P[31:25] specifically with no calculation, that can diminishes the exchanging power. On the off chance that the info convey bit Cin =1then, the yield of the multiplexer is the expansion of the fractional item yield p3[15:9] with the convey bit utilizing half adders. The last do bit (Cout) is disposed of in the last item.

The utilization of the quick viper in the proposed configuration enhances the execution as far as postponement, and power-defer item. Consequently, the flag handling can be made quicker utilizing the proposed multiplier in Multiplier-Accumulator (MAC) unit, Fast Fourier Transform (FFT), convolution, and separating. Nonetheless, the real downside of the proposed multiplier is that, it requires bigger territory for calculation.

TABLE I. Union REPORT

| Parameter                  | Booth Multiplier | Vedic Multiplier using<br>Brent-kung Adder | Vedic Multiplier using<br>Kogge-stone Adder |

|----------------------------|------------------|--------------------------------------------|---------------------------------------------|

| Number of 4 input<br>LUT's | 41               | 27                                         | 31                                          |

| Number of IO's             | 16               | 32                                         | 32                                          |

| Number of Slices           | 21               | 15                                         | 16                                          |

| Delay(ns)                  | 15.647           | 17.507                                     | 15.02\$                                     |

| Power(mW)                  | 56               | 56                                         | 36                                          |

| Power Delay<br>Product(pj) | \$76             | 980                                        | 841                                         |

For correlation, we have executed different multipliers whose fractional item bits are included by utilizing distinctive methodologies. These multipliers were displayed in VHDL utilizing XILINX 10.1 variant.

## IV. CONCLUSION

In this paper, we exhibited a Vedic multiplier to limit the power-defer result of 8-bit multipliers for elite applications. In the proposed multipliers, the summation of halfway results of Vedic multiplier was marginally adjusted utilizing convey spare snake, kogge-stone viper, and convey select viper with a specific end goal to enhance the proficiency of the multipliers. Test comes about have exhibited that the proposed multiplier with quick adders can accomplish huge change in deferral and power-

postpone item when contrasted and the ordinary multiplier models.

### **REFERENCES**

- [1] J. Pihl and E. J. Aas, "A multiplier and squarer generator for high performance DSP applications," in Circuits and Systems, 1996., IEEE 39th Midwest symposium on, vol. 1. IEEE, 1996, pp. 109–112.

- [2] H. Guilt, "Fully iterative fast array for binary multiplication," Electronics Letters, vol. 5, p. 263, 1969.

- [3] T. G. Noll, "Carry-save architectures for high-speed digital signal processing," Journal of VLSI signal processing systems for signal, image and video technology, vol. 3, no. 1-2, pp.121–140, 1991.

- [4] G.Goto, T.Sato, M.Nakajima and T.Sukemura, "A54×54-b regularly structured tree multiplier, "Solid-State Circuits, IEEE Journal of, vol.27, no. 9, pp. 1229–1236, 1992.

- [5] G.Goto, "High speed digital parallel multiplier," Nov. 7 1995, us Patent 5,465,226.

- [6] A. D. Booth, "A signed binary multiplication technique," The Quarterly Journal of Mechanics and Applied Mathematics, vol. 4, no. 2, pp. 236–240, 1951.

- [7] A. Cooper, "Parallel architecture modified Booth multiplier," Electronic Circuits and Systems, IEE Proceedings G, vol. 135, no. 3, pp. 125–128, 1988.

- [8] J. Fadavi-Ardekani, "M\*N Booth encoded multiplier generator using optimized Wallace trees," Very Large Scale Integration (VLSI) Systems, IEEE Transactions on, vol. 1, no. 2, pp. 120–125, 1993.